Nella vita di tutti i giorni utilizziamo costantemente apparecchi elettronici il cuore dei quali, nella maggior parte dei casi, è il processore. Il processore è un chip, un microcomponente informatico formato da milioni di transistor, dedicato all’esecuzione di istruzioni, la cui realizzazione è complessa ed affascinante. Quest’articolo è tratto da una guida della Intel Corporation dedicata alle fasi di costruzione di un processore Intel Core i5 di seconda generazione, costruito con una tecnologia a 22 nm.

Il silicio è il secondo materiale per diffusione nella crosta terrestre. La sabbia comune ha un’elevata percentuale di silicio. Il silicio – il materiale di base per la costruzione di chip elettronici – è un semiconduttore che può essere velocemente trasformato in un eccellente conduttore o isolatore di elettricità, grazie all’inserimento di piccolissime impurità.

Il silicio è il secondo materiale per diffusione nella crosta terrestre. La sabbia comune ha un’elevata percentuale di silicio. Il silicio – il materiale di base per la costruzione di chip elettronici – è un semiconduttore che può essere velocemente trasformato in un eccellente conduttore o isolatore di elettricità, grazie all’inserimento di piccolissime impurità.

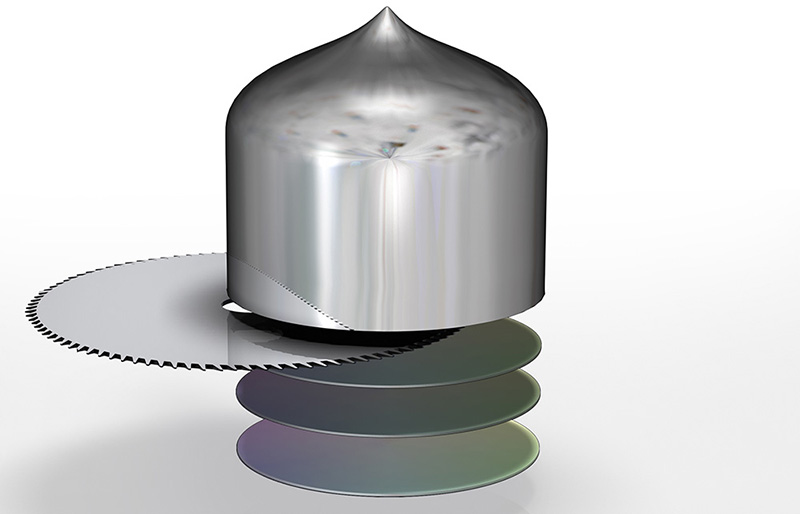

Per essere utilizzato nella costruzione di chip elettronici, il silicio deve essere purificato in maniera tale da contenere meno di un atomo impuro ogni due miliardi. Il silicio viene tirato da uno stato fuso fino a formare un solido costituito da un singolo, continuo ed ininterrotto reticolo cristallino di forma cilindrica, chiamato lingotto.

Il lingotto ottenuto ha un diametro di 300 mm. (12 pollici) e pesa circa 100 kg.

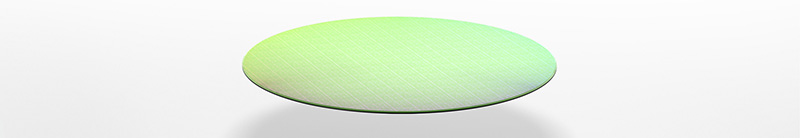

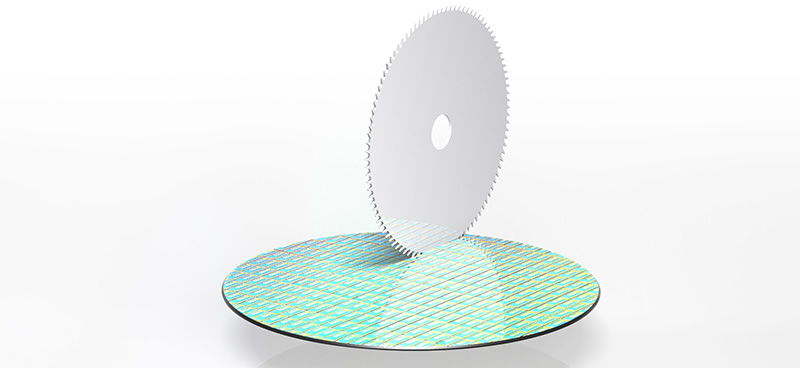

Il lingotto viene tagliato in dischi di silicio chiamati wafer. Ciascun wafer ha un diametro di 300 mm. ed uno spessore di circa 1 mm.

I wafers vengono trattati e puliti fino ad avere una superficie perfetta e a specchio. La dimensione dei wafers è aumentata nel tempo, consentendo di ridurre i costi di produzione di un singolo chip. Quando Intel ha iniziato a produrre chips, esistevano solo wafers del diametro di 50 mm. Attualmente si utilizzano wafers del diametro di 300 mm. ed è previsto, in futuro, l’utilizzo di wafers del diametro di 450 mm. Aumentando le dimensioni del wafer, aumenta il numero di chips che il singolo wafer può ospitare e diminuisce il tempo di produzione, consentendo una riduzione dei costi.

La costruzione di chips elettronici su un wafer è il risultato di centinaia di passaggi estremamente precisi che consiste nel sovrapporre una serie di strati di vari materiali uno sull’altro.

Di seguito riassumeremo i passaggi più significativi di questo complesso processo.

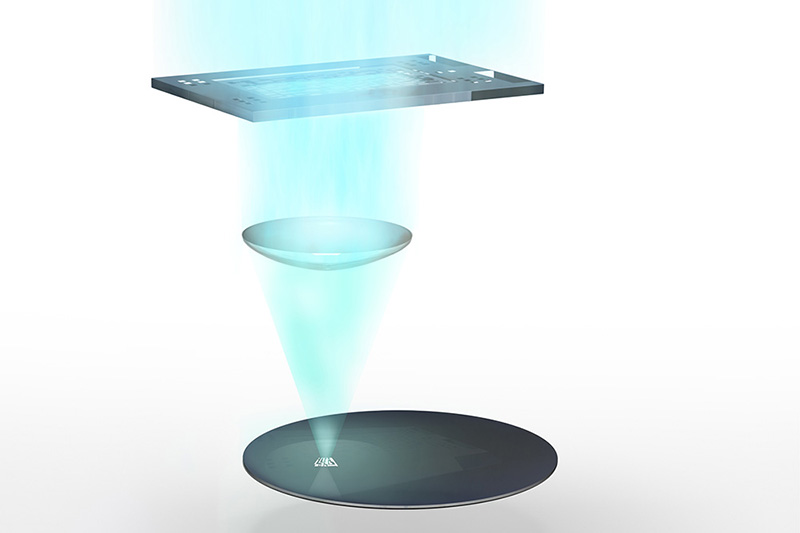

La fotolitografia è il processo mediante il quale uno specifico disegno viene stampato sul wafer. Tale processo inizia con l’applicazione di un liquido noto come fotoresistente che viene uniformemente versato sul wafer mentre ruota per assicurarne una distribuzione uniforme sulla superficie. Il nome fotoresistente deriva dal fatto che esso è sensibile ad alcune frequenze di luce (foto) e resistente ad alcune sostanze chimiche che verranno utilizzate successivamente per rimuovere porzioni di strato del materiale (resistente).

Il fotoresistente viene fatto indurire, ed alcune porzioni di esso vengono esposte ad una luce ad ultravioletti che lo rende solubile. L’esposizione viene effettuata usando delle maschere che agiscono come stampi, in maniera da rendere solubili solamente delle specifiche porzioni del fotoresistente. La maschera contiene un’immagine del disegno che deve essere trasferito sul wafer. Essa viene otticamente ridotta da una lente, e la fase di esposizione viene ripetuta più volte sul wafer per formare la stessa immagine più volte, una per ciascun chip ospitato dal wafer.

Il fotoresistente solubile viene rimosso con un processo chimico, e viene lasciato uno strato di fotoresistente determinato dal disegno contenuto nella maschera.

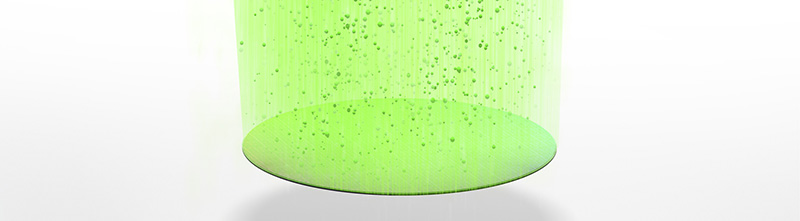

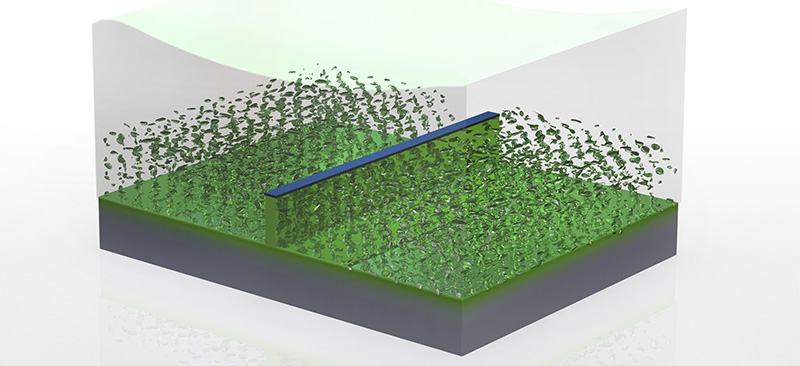

Il wafer con il fotoresistente impresso viene bombardato da un fascio di ioni (atomi con carica positiva o negativa) che diventa incorporato sotto la superficie negli spazi non coperti dal fotoresistente. Questo processo è chiamato doping, in quanto vengono introdotte nel silicio delle impurità. Questo processo altera le proprietà conduttive del silicio (rendendolo conduttivo o isolante a seconda del tipo di ioni usati) in ben determinate aree. Qui illustriamo la creazione dei pozzi, che sono aree all’interno delle quali verranno realizzati i transistors.

In seguito all’impiantazione ionica, il fotoresistente viene rimosso, ed il risultato sarà un wafer con aree dopate nelle quali verrà realizzato il transistor.

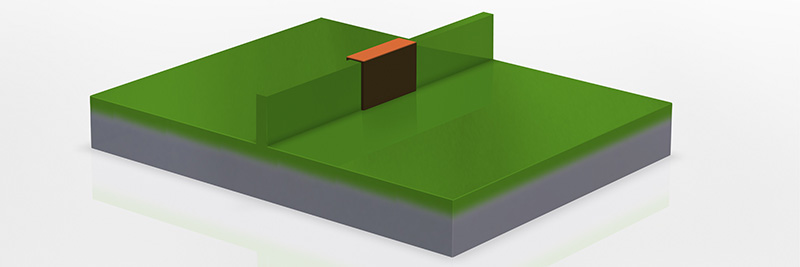

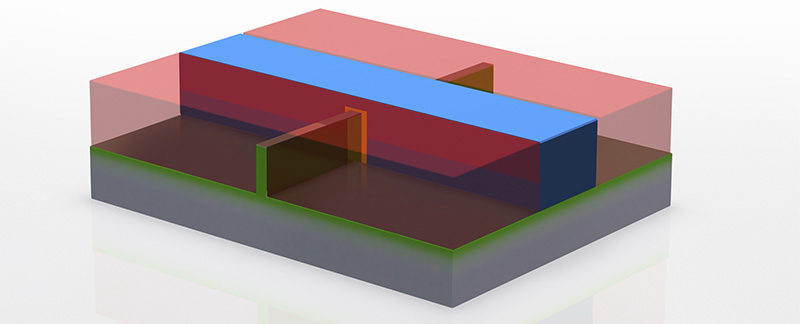

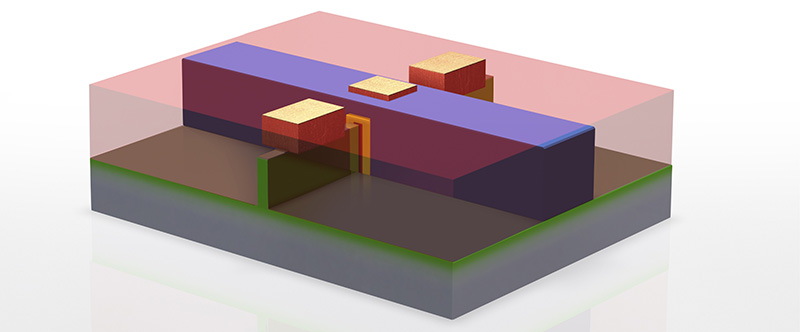

In quest’immagine ingrandiamo una piccola parte del wafer, nella quale verrà realizzato un singolo transistor.

L’area verde rappresenta il silicio dopato. I wafer possono ospitare centinaia di miliardi di aree simili.

Per creare una pinna per un transistor di tipo tri-gate, viene applicato, usando il processo fotolitografico precedentemente descritto, uno stampo di materiale chiamato “hard mask” (blu nella foto). Successivamente viene applicato un agente chimico per rimuovere il silicio indesiderato, lasciando una pinna con uno strato di “hard mask” sopra.

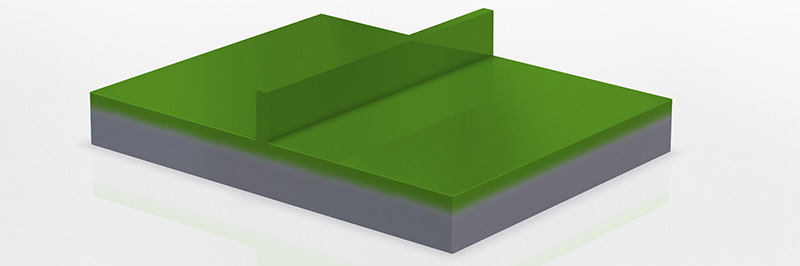

L’ ”hard mask” viene rimossa chimicamente, lasciando una pinna alta e sottile che conterrà il canale di un transistor.

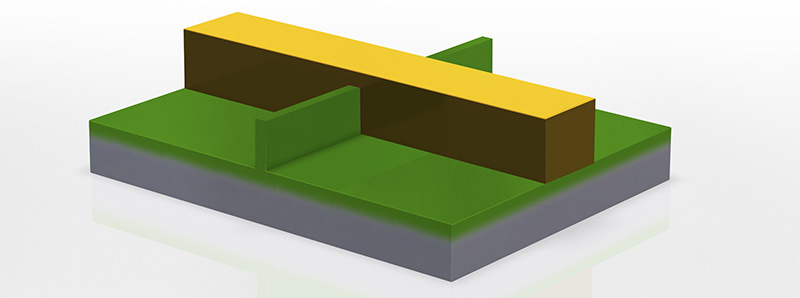

Con un successivo processo di fotolitografia, porzioni del transistor vengono coperte con del fotoresistente ed un sottile strato di biossido di silicio (rosso nella foto) viene creato inserendo il wafer in una fornace a tubolare piena di ossigeno.

Un ulteriore processo di fotolitografia permette di creare uno strato temporaneo di silicio policristallino (giallo nella foto). Esso diventerà un cancello elettrodo temporaneo.

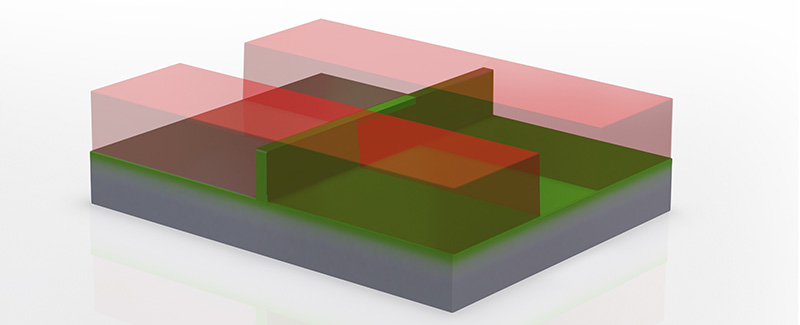

In un successivo processo di ossidazione, uno strato di biossido di silicio viene posto su tutto il wafer (rosso trasparente nella foto) per isolare il transistor dagli altri elementi.

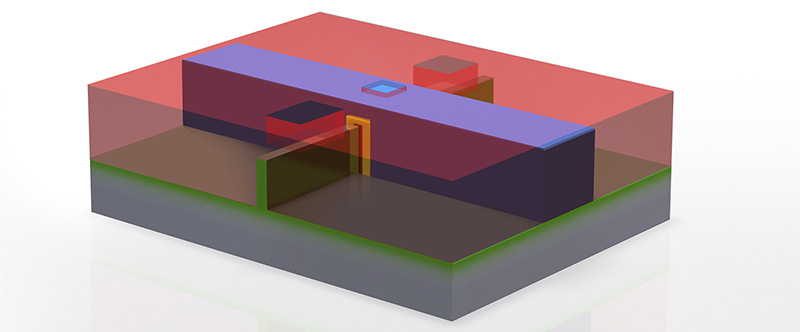

Intel utilizza una tecnica “gate last” (anche nota con il nome di “sostituzione del cancello metallico”) per creare i suoi transistor. Questo viene fatto per evitare problemi di stabilità del transistor che potrebbero verificarsi in alcune successive fasi ad alta temperatura del processo di produzione.

Attraverso un’operazione di mascheratura, il cancello temporaneo viene rimosso per fare spazio a quello definitivo. Il nome “Gate last” deriva proprio dall’eliminazione di questo cancello temporaneo.

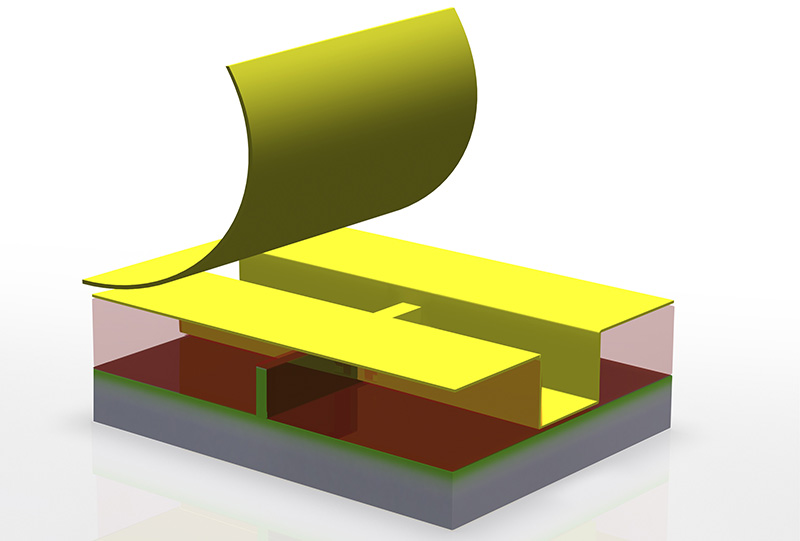

Strati molecolari individuali vengono applicati alla superficie del wafer in un processo chiamato deposizione atomica dello strato. Gli strati gialli rappresentati nella foto ne sono un esempio. Attraverso un processo fotolitografico il materiale “high-k” viene rimosso dalle aree indesiderate.

Un cancello di metallo elettrodo (blu nella foto) viene creato sul wafer e, utilizzando un processo di fotolitografia, rimosso dalle regioni indesiderate. La combinazione del cancello di metallo con il materiale di tipo “high-k” (sottile strato giallo) consente al transistor di offrire migliori prestazioni e minore dispersione.

Il transistor è quasi completo. Sono stati incisi tre fori nello strato isolante (rosso nella foto) sopra il transistor. Questi fori saranno riempiti con del rame per permettere la connessione con altri transistors.

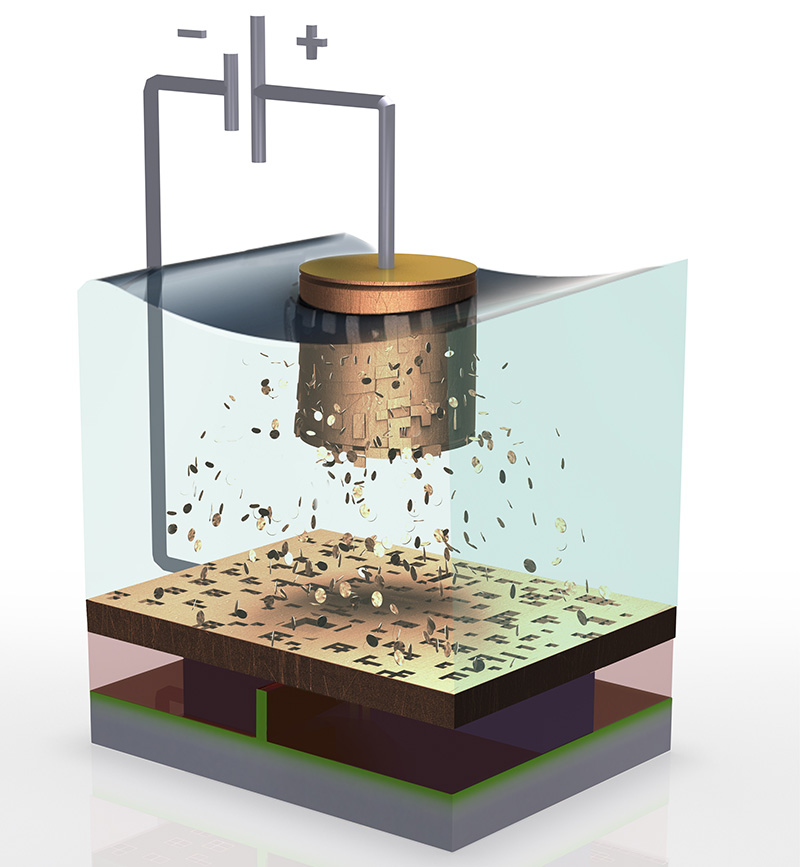

I wafers vengono immersi in una soluzione di solfato di rame. Gli ioni di rame vengono depositati sul transistor. Gli ioni di rame viaggiano dall'anodo positivo al catodo negativo che è il wafer.

Gli ioni di rame si depositano sulla superficie del wafer formando un sottile strato di rame.

L’eccesso di materiale viene rimosso meccanicamente per rivelare specifiche aree di rame.

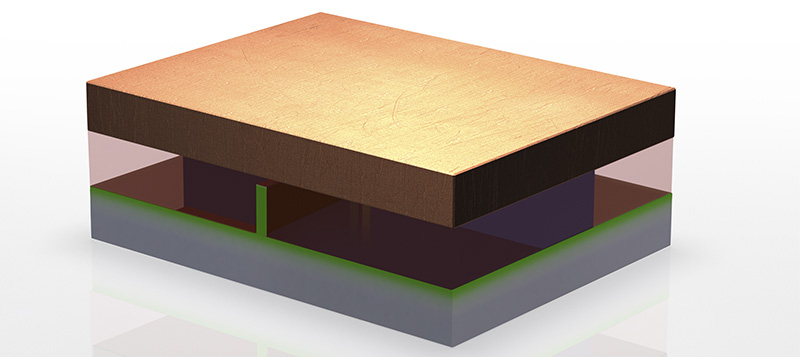

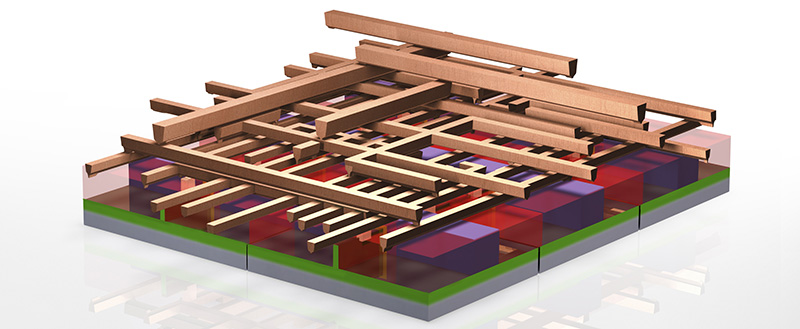

Strati metallici multipli vengono creati per connettere tra di loro tutti i transistors che compongono il chip. Il modo in cui vengono create queste connessioni viene determinato dai progettisti del chip. Sebbene i chips dei computer sembrino estremamente piatti, possono contenere più di 30 strati di circuiti.

Una vista ingrandita di un chip mostrerà un complesso sistema di connessioni e transistors simile ad un futuristico sistema autostradale.

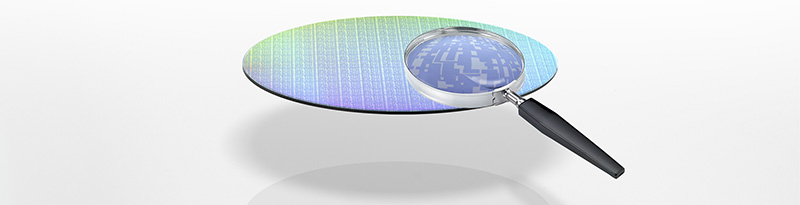

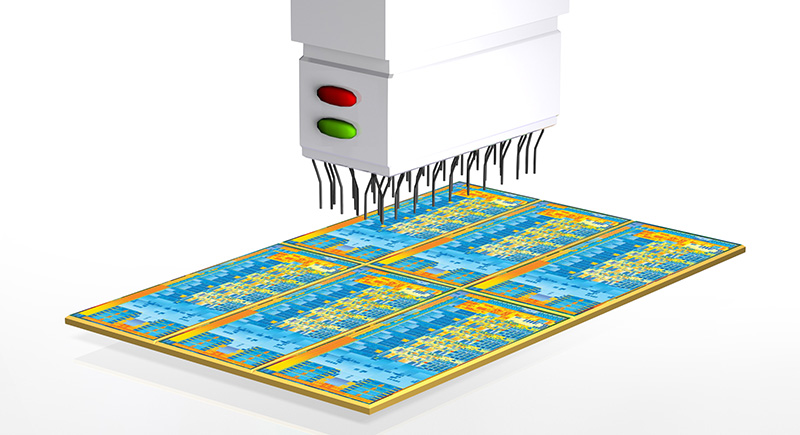

Quando il processo di costruzione del wafer è finito, i wafers vengono trasferiti in uno stabilimento di Test ed Assemblaggio. Qui i wafer vengono testati e successivamente tagliati in modo che ogni singolo chip possa essere di nuovo testato, impacchettato e spedito.

Qui sopra vediamo una porzione di wafer sottoposta a test. Un tester si muove sopra il wafer controllando ogni singolo chip mediante un test elettrico. Chips difettosi vengono segnalati per lo scartamento successivo.

Il wafer viene tagliato dividendo ed isolando i singoli chips (chiamati “die”).

I chips che rispondono ai requisiti di progettazione vengono inviati all’imballaggio.

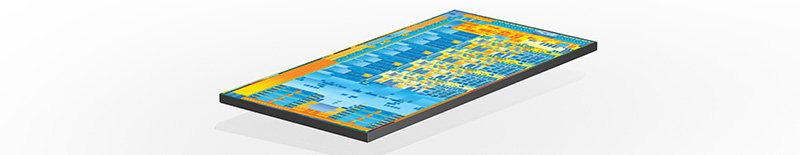

Nella foto sopra viene mostrato un chip che compone il primo processore Intel Core i5 con tecnologia a 22 nm chiamato con il nome di “Ivy Bridge”.

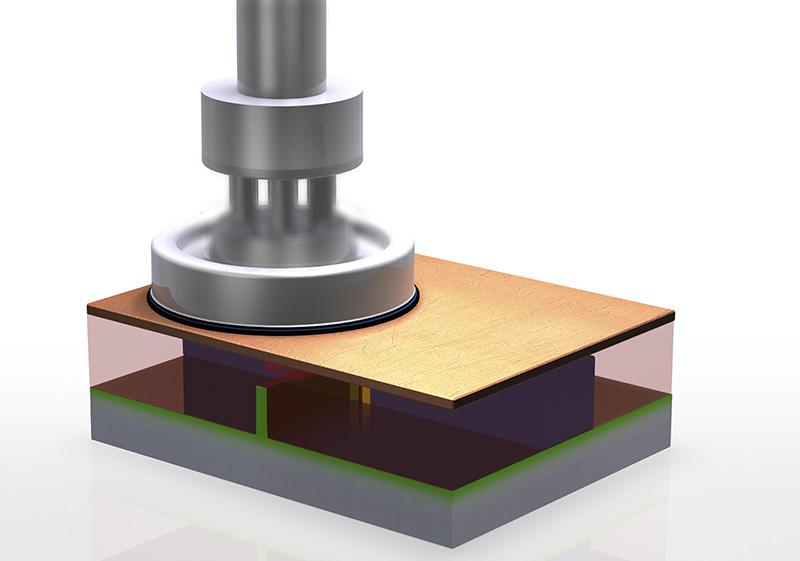

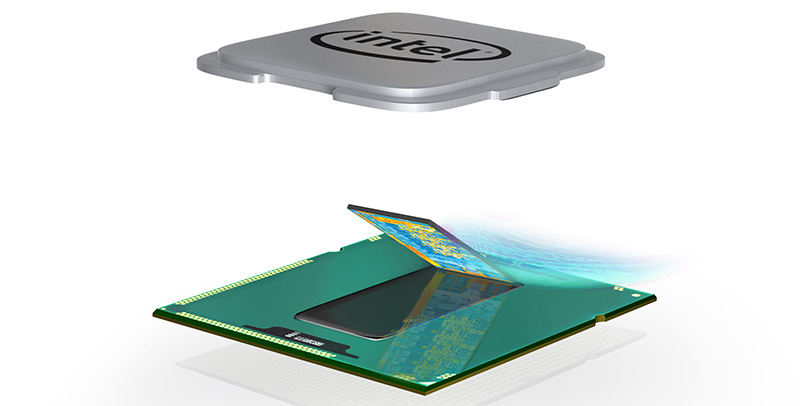

Il chip viene assemblato con un substrato e con un diffusore di calore a formare il processore completo. Il substrato verde costituisce l’interfaccia elettrica e meccanica attraverso la quale il processore interagisce con la scheda madre. Il diffusore di calore color argento serve, insieme ad una ventola, a dissipare il calore.

Ecco un microprocessore “Ivy Bridge” completo. Un microprocessore è uno dei prodotti manufatturieri più complessi costruito dall’uomo. Per la sua creazione sono necessari infatti centinaia di passaggi. In quest’articolo sono stati mostrati solo quelli più rilevanti.

Durante questo test finale il microprocessore viene completamente testato nelle sue funzionalità, prestazioni e potenza.

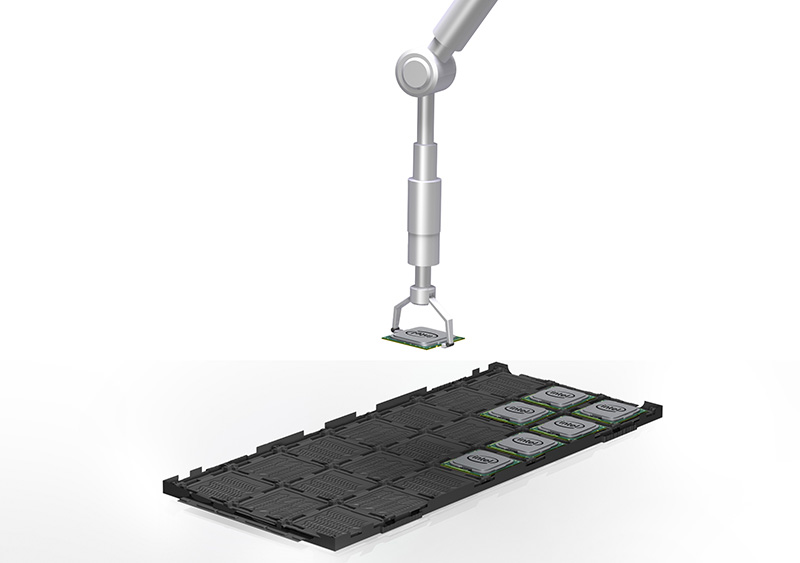

In base ai risultati ottenuti nel test della classe, i processori con uguali capacità vengono impacchettati insieme in contenitori destinati ai produttori di computer.

I processori destinati alla vendita nei negozi vengono invece confezionati in apposite scatole.

I wafer ed i chip vengono costruiti in apposite fabbriche chiamate Wafer Fab che rispondono a severissimi standard di progettazione. Per costruire microprocessori servono principalmente due condizioni: una pulizia dell’aria superiore a quella di una sala operatoria ed una stabilità statica dell’edificio assoluta per evitare che qualsiasi vibrazione esterna possa compromettere un processo produttivo che agisce su dimensioni infinitesimali.

Il processo di costruzione di un wafer dura più giorni, per questo i Wafer Fab lavorano 24 ore al giorno senza interruzioni. In un prossimo articolo parlerò proprio dei Wafer Fab, sulla base delle esperienze personalmente maturate collaborando da anni come responsabile grafico ed informatico del più prestigioso studio di architettura specializzato nella progettazione di questi affascinanti edifici.

Il contenuto di quest’articolo si basa su una pubblicazione della Intel Corporation che potete consultare in lingua originale inglese, a questo link.

La stesura di questo articolo ha richiesto molto tempo. Se lo hai trovato utile e vuoi cliccare su Mi piace o Condividi mi farai cosa gradita. Grazie.

© 2014 - Intel Corporation. Tutte le immagini sono di proprietà di Intel Corporation.

© 2014 - Michele Angeletti - Via Antonio Fogazzaro, 10 - 00137 - Roma

Tel: 06.82.78.681 - 335.78.74.178